南京做网站具体需要多少钱营销的概念是什么

一.前言

最近课设又用到了STM32方面的知识,由于有段时间没使用,突然发现有很多地方已经很生疏了,复习起来又比较麻烦,灵光一闪,索性开个博客记录自己学习的历程,而且有点想锻炼一下自己的能力,减轻类似教程之类的依赖,锻炼自己读参考手册和数据手册的能力,对于以后的复习也会大有帮助,先起个头,以后写点什么都不一定。

二.定时器基本介绍

一)定时器主要功能

正好手头有老师发的STM32F746的开发板,就先拿这个做个例子。

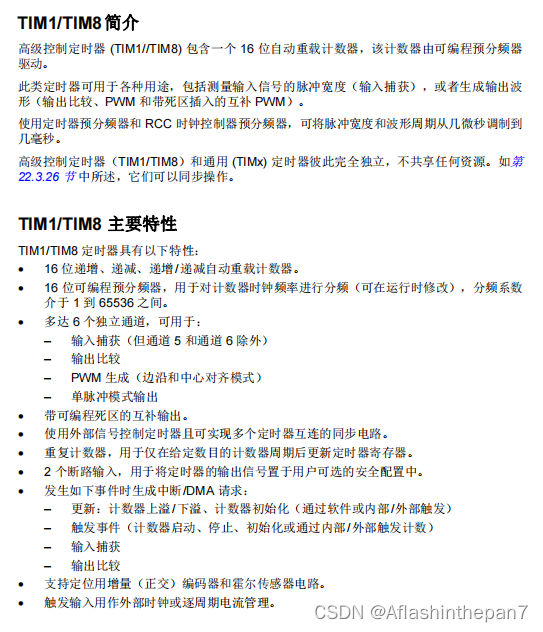

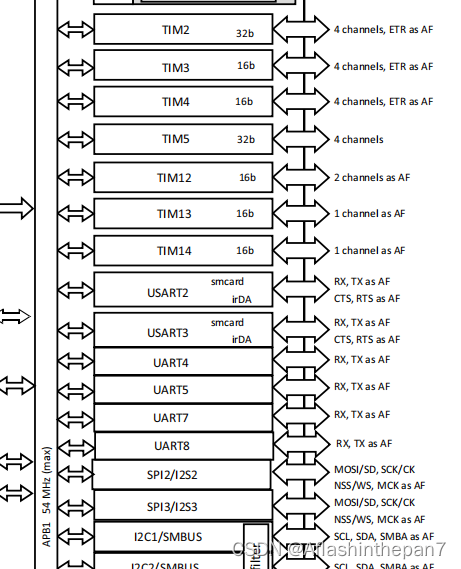

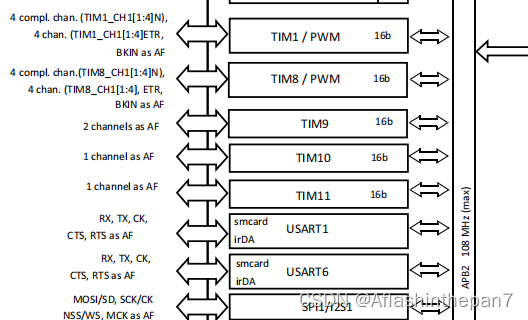

从参考手册可以看到,STM32F746NGH6这个芯片共有14个TIM定时器,又分成高级定时器、通用定时器、基础定时器,高级定时器的功能更加复杂,更强大。

![]()

![]()

![]()

![]()

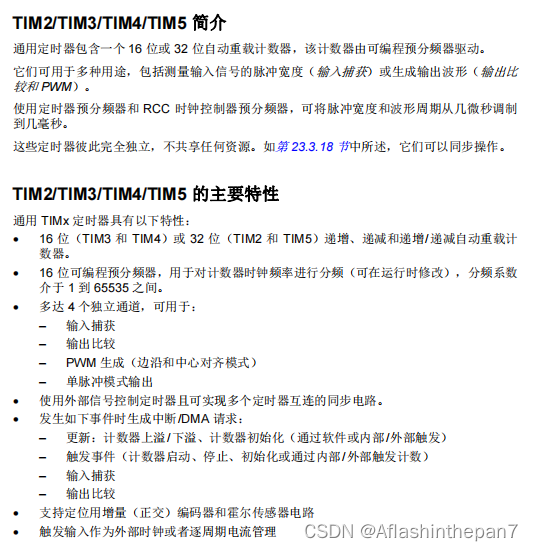

对比之下,高级定时器有捕获/比较通道和互补输出,通用定时器只有捕获/比较通道,基本定时器没有以上两者,从参考手册可以了解。

可以从参考手册中看到,定时器之间还有一些像计数器位数、通道之类的区别,高级定时器最大的特点在于有死区插入的互补(两路完全反向的PWM)输出模式,该种输出可以用于电机控制(暂时没有了解太多)。

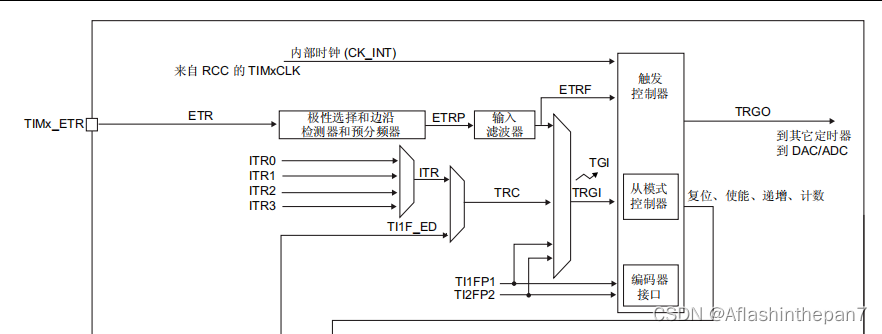

二)时钟源

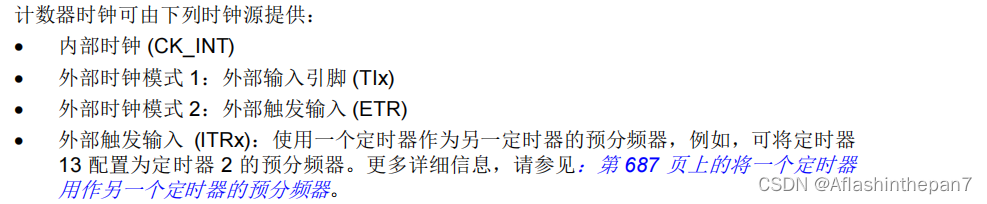

作为定时器,最根本的在于它到底靠什么计数,计数器根据其所用的时钟源,每个周期执行+1或者-1的操作来实现计数功能,再根据各种寄存器实现不同的输出,所以在配置计数器之前,了解计数器的时钟源是最重要的,时钟源可以选择四种方式。

如下图,分别是①内部时钟(CK_INT) ②外部时钟模式:外部触发输入(ETR) ③内部触发输入(ITRx):使用一个定时器作为另一个定时器的预分频器,如可以配置一个定时器Timer1而作为另一个定时器Timer2的预分频器。 ④外部时钟模式:外部输入脚(TIx)。其中最常用的是内部时钟源,主要学习该方式的原理和配置。

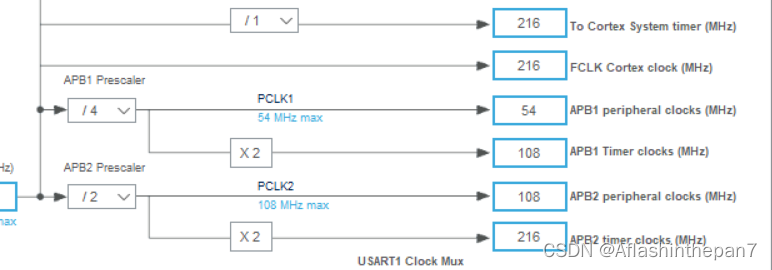

对于内部时钟,使用的是时钟TIMxCLK(CK_INT),该时钟由APBx经过预分频再倍频×2后得到的。

所以首先要先知道对应的TIMxCLK是挂在哪条总线的,阅读数据手册,下图

可以看到,TIM1/8/9/10/11是挂在总线APB2上面的,TIM2/3/4/5/12/13/14是挂在总线APB1上的,所以根据总线的频率配置对应所需的定时器即可。

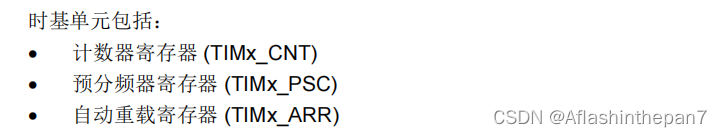

三)时基单元

可编程定时器的主要模块由一个 16 位/32 位计数器及其相关的自动重装寄存器组成。计数器可递增计数、递减计数或同时递增和递减计数。计数器的时钟可通过预分频器进行分频。 计数器、自动重载寄存器和预分频器寄存器可通过软件进行读写。即使在计数器运行时也可执行读写操作。所谓时基单元,我们来看参考手册给的解释

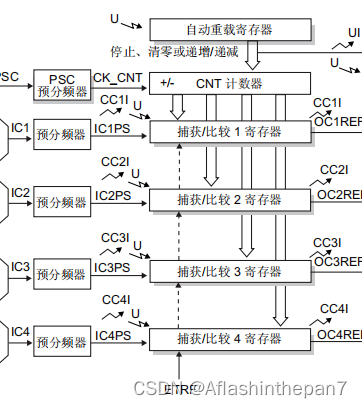

对应着定时器框图中的这部分

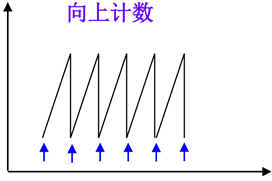

首先是计数器寄存器,具有上计数、下计数、 中心对齐计数等方式,储存计数值,而计数器寄存器的计数时钟(CK_CNT)是由计数器的时钟源周期(CK_INT)和预分频器寄存器决定的,CK_CNT=CK_INT / PSC。

四)定时器的触发

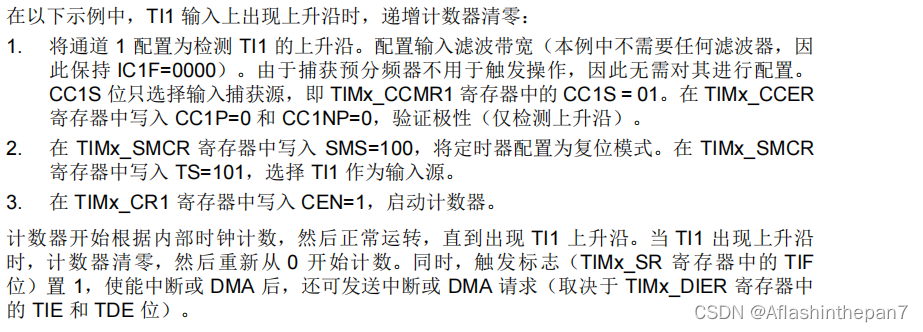

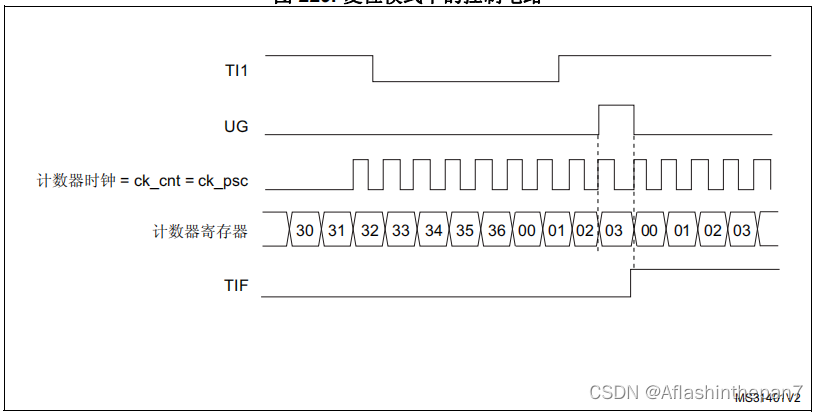

1. 从模式: 复位模式

当触发输入信号发生变化时,计数器及其预分频器可重新初始化。此外,如果 TIMx_CR1 寄存器中的 URS 位处于低电平,则会生成更新事件 UEV。然后,所有预装载寄存器(TIMx_ARR 和 TIMx_CCRx)都将更新。即触发信号变化, 下图为示例。

时钟图如下,TI1 的上升沿与实际计数器复位之间的延迟是由于 TI1 输入的重新同步电路引起的。

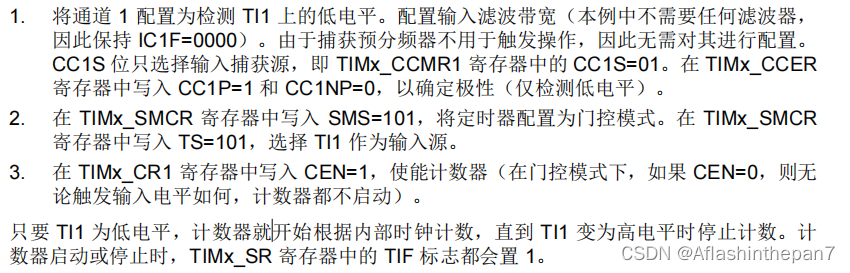

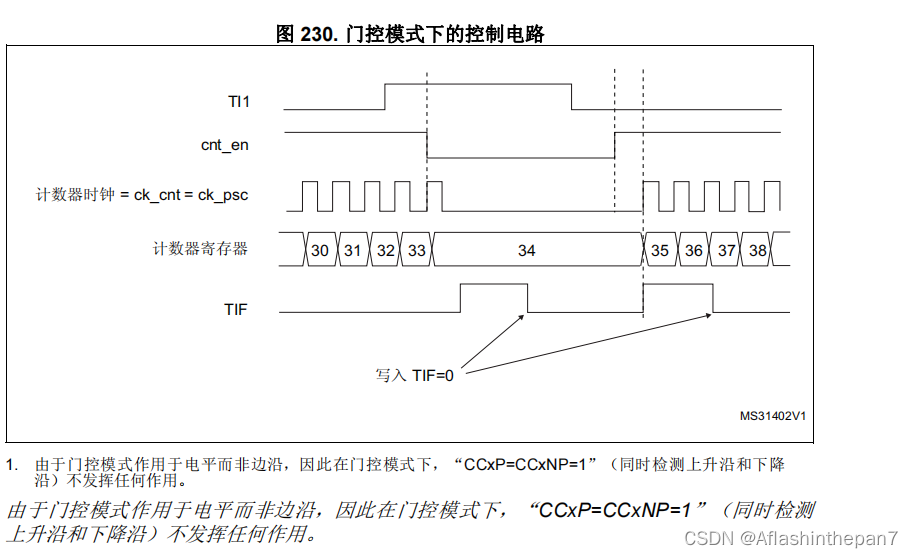

2.从模式:门控模式

输入信号的电平可用来使能计数器。 在以下示例中,递增计数器仅在 TI1 输入为低电平时计数:

时钟图如下,TI1 的上升沿与实际计数器停止之间的延迟是由于 TI1 输入的重新同步电路引起的。

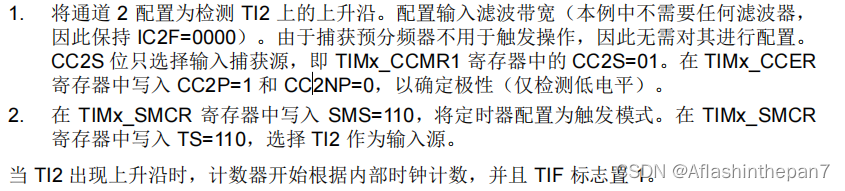

3.触发模式

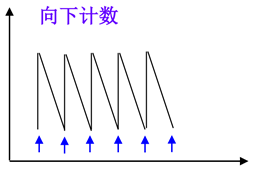

所选输入上发生某一事件时可以启动计数器。在以下示例中,TI2 输入上出现上升沿时,递增计数器启动:

时钟图如下,TI2 的上升沿与实际计数器启动之间的延迟是由于 TI2 输入的重新同步电路引起的。

三.计数器模式

一)计数模式

1.增计数模式

在递增在递增计数模式下,计数器从 0 计数到自动重载值(TIMx_ARR 寄存器的内容),然后重新从0开始计数并生成计数器上溢事件,每次溢出以后会生成更新时间,或将TIMx_EGR寄存器中的UG位置1。

但是增计数存在一种隐患,例如原本的重装载寄存器(TIMx_ARR)为5,然后在计数过程中计数器寄存器计数到了4,此时代码中运行将重装载寄存器更新为3,这样会导致此次计数将会计数到计数器寄存器的上限,即65535,造成一次计数周期的错误。

解决这个问题有两种方法,一是采用减计数模式,二是使能影子寄存器,在一次计数周期内,即使代码改变了重装载寄存器,此次计数周期仍采用原来的比较值,解决了该问题。

2.减计数模式

3.中心对其模式(递增/递减模式)

二)输入捕获模式

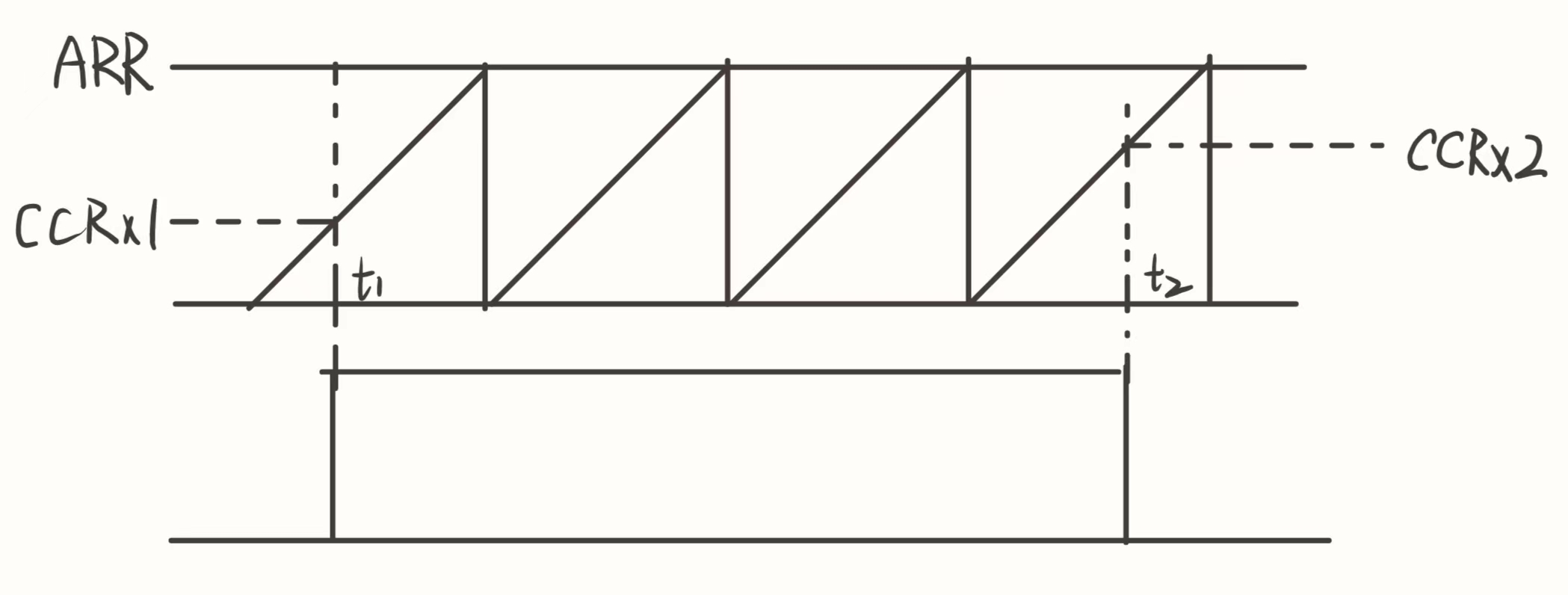

三)PWM输入模式

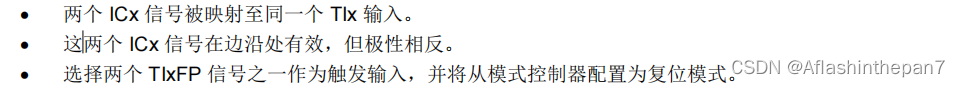

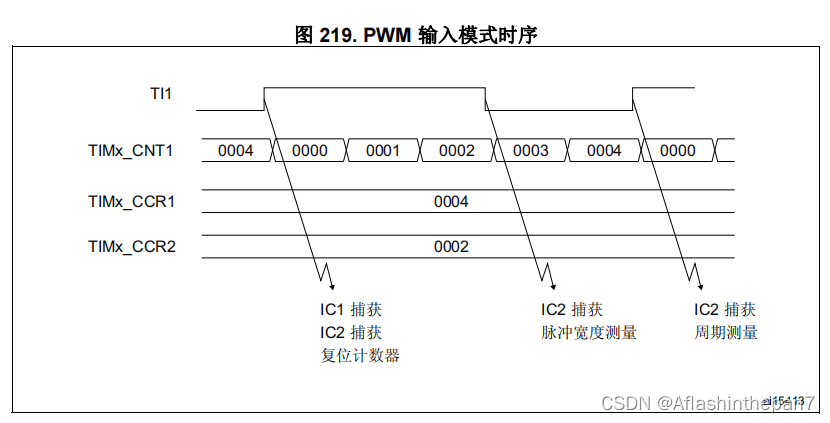

此模式为输入捕获模式的一个特例,配置方式基本一致,仅存在部分区别,从参考手册可以得出

即在输入捕获的基础上使用两组输入捕获通道对同一个TIM引脚进行捕获。

从时序图中也可以看出,IC1和IC2信号都映射到了TI1引脚,在TI1引脚输入的信号,在第一次上升沿触发了两次捕获,然后在随后的下降沿触发了IC1的捕获,又在下一个上升沿触发了IC2的捕获.(参考手册的图好像有点问题。。。)这样可以轻易的测量出信号的占空比、周期等参数。

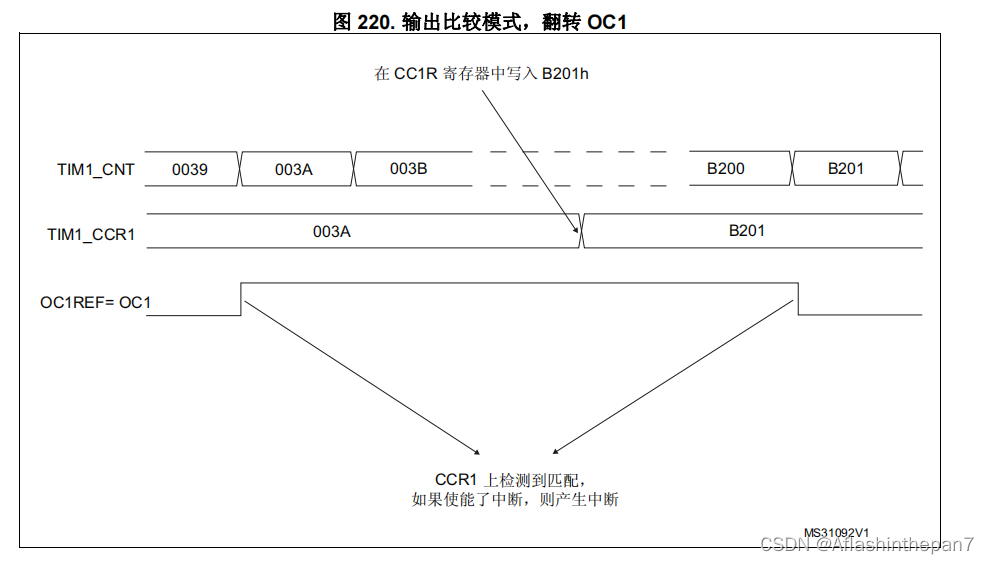

四)输出比较模式

这个模式最常用,一般用来控制输出的波形或者指示已经过了某个时间段。还是先看参考手册的介绍。

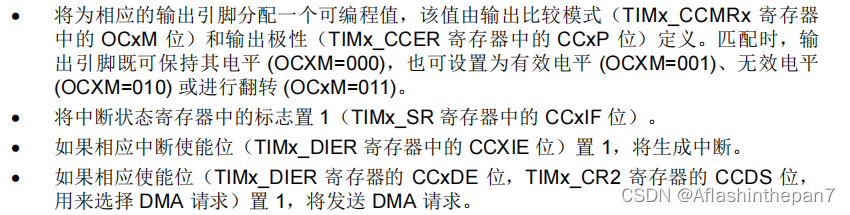

当捕获/比较寄存器与计数器之间相匹配时,输出比较功能:

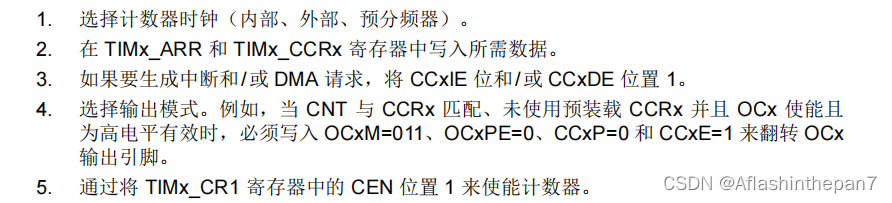

可以控制电平、生成中断、开启DMA等,可以通过CCMRx寄存器与CCER寄存器的关系来对输出电平进行置1,置0或翻转的操作,用于输出一定频率和占空比的PWM波形。配置流程如下

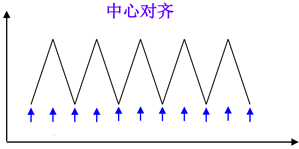

先选择时钟源,再配置预分频器,写入重装载寄存器(ARR)和比较/捕获寄存器(CCRx) ,如果有需要配置中断和DMA,选择输出模式,最后开启定时器,下图为时序图。

五)PWM模式

和输出比较模式类似,通过时钟源频率和重装载寄存器(TIMx_ARR )控制PWM的周期,通过捕获/比较寄存器(TIMx_CCRx)控制占空比。根据 TIMx_CR1 寄存器中的 CMS 位状态,定时器能够产生边沿对齐模式或中心对齐模式的PWM 信号。

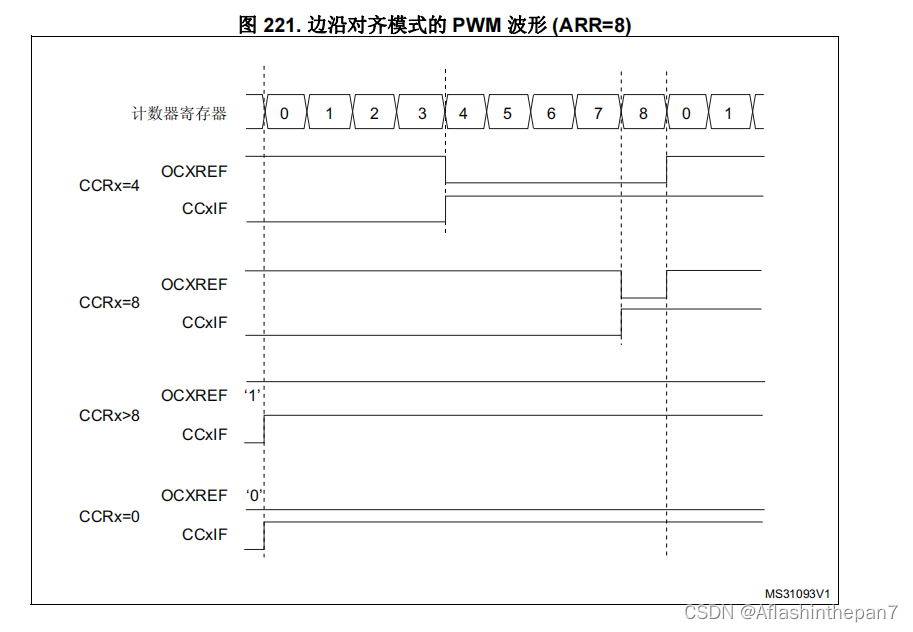

PWM边沿对齐模式

递增计数时

计数器为增计数模式时,当只要 TIMx_CNT (计数器寄存器)< TIMx_CCRx(捕获/比较寄存器),PWM 参考信号 OCxREF 便为高电平,否则为低电平。

如果 TIMx_CCRx 中的比较值大于自动重载值(TIMx_ARR 中),即计数器溢出时, 则 OCxREF 保持为“1”。如果比较值为 0,则 OCxREF 保持为“0”。话不多说,直接上时序图,简洁明了。(CCxIF为中断)

从图中可以轻松看出,计数器计数值小于捕获比较寄存器时输出PWM为高电平,然后在等于的计数周期到来的跳变沿,输出PWM翻转为低电平,再到计数器溢出的下一个计数周期到来的跳变沿翻转为高电平,由此来控制周期和占空比。

递减计数时

计数器为减计数模式,在 PWM 模式 1 下,只要 TIMx_CNT>TIMx_CCRx,参考信号 ocxref 便为低电平,否则为高电平。如果 TIMx_CCRx 中的比较值大于 TIMx_ARR 中的自动重载值,则 ocxref 保持为 “1”。此模式下不可能产生 0% 的 PWM 波形。

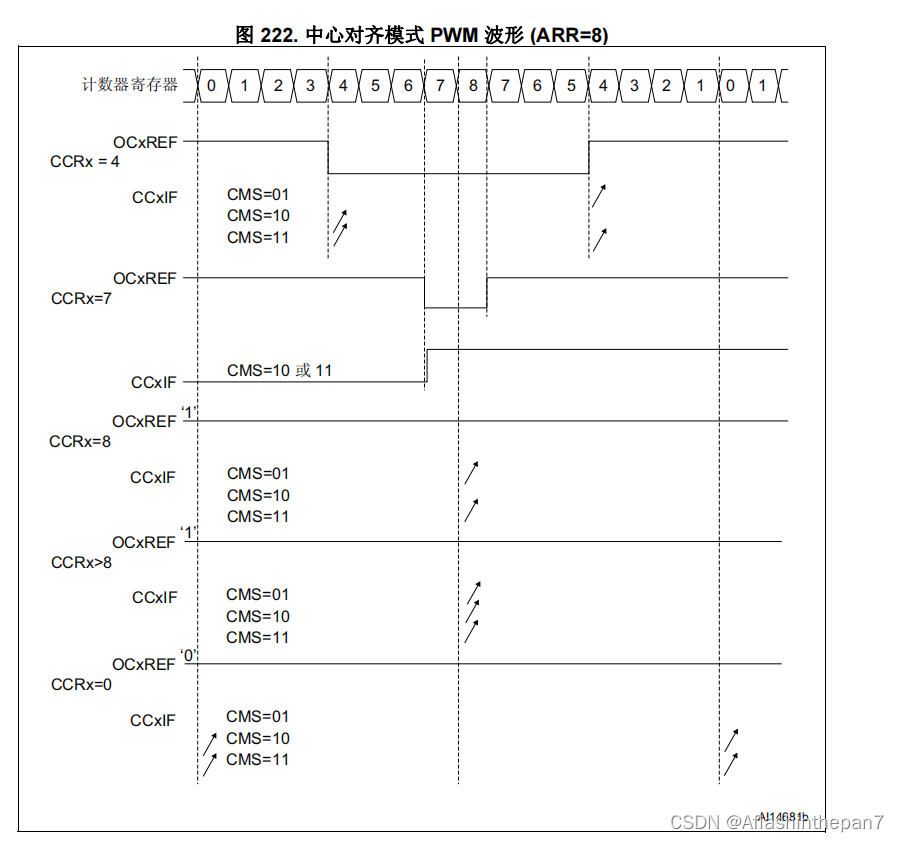

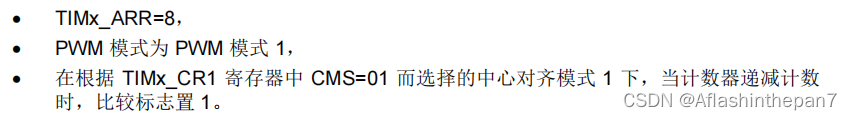

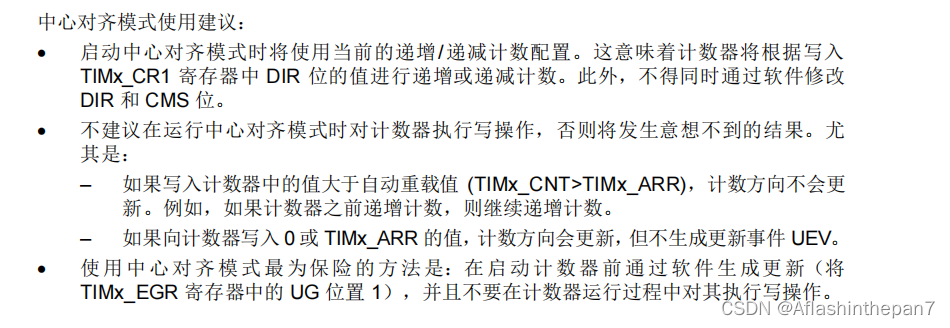

PWM中心对齐模式

计数器为中心对齐计数方式,还是直接上时序图。

六)单脉冲模式

六)单脉冲模式

在这种模式下,计数器可以在一个激励信号的 触发下启动,并可在一段可编程的延时后产生一个脉宽可编程的脉冲。可以通过从模式控制器启动计数器。可以在输出比较模式或 PWM 模式下生成波形。将TIMx_CR1 寄存器中的 OPM 位置 1,即可选择单脉冲模式。这样,发生下一更新事件 UEV 时,计数器将自动停止。只有当比较值与计数器初始值不同时,才能正确产生一个脉冲。

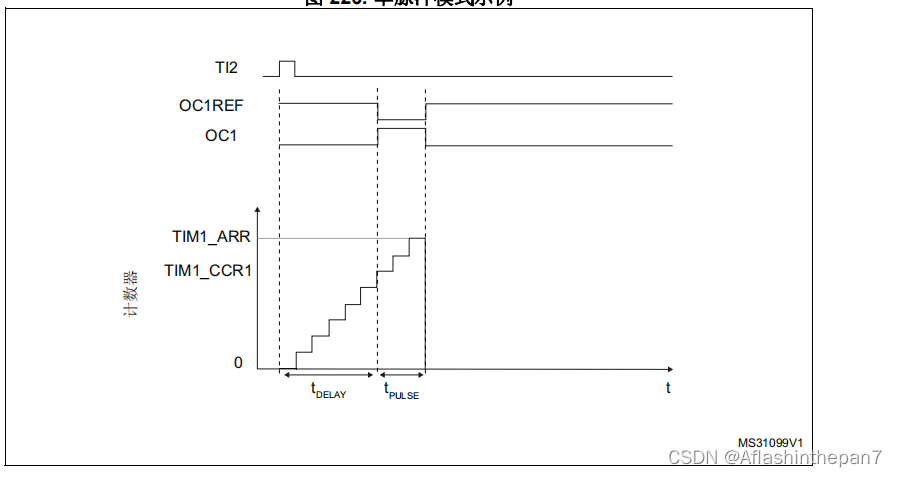

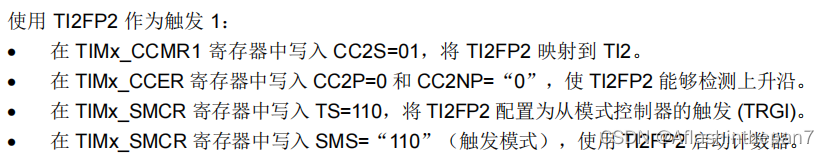

考虑这样一个场景,用户希望达到这样的效果:在 TI2 输入引脚检测到上升沿时,经过 tdelay 的延迟,在OC1 上产生一个长度为 tpulse 的正脉冲。

触发以后,当计数器小于比较捕获寄存器(CCR1)时,即为延时时间,当计数器大于比较捕获寄存器(CCR1),小于重装载寄存器(ARR)时,为正脉冲时间。

由于仅需要 1 个脉冲(单脉冲模式),因此应向 TIMx_CR1 寄存器的 OPM 位写入“1”, 以便在发生下一更新事件(计数器从自动重载值返回到 0)时使计数器停止计数。TIMx_CR1 寄存器中的 OPM 位置“0”时,即选择重复模式。

四.总结

STM32功能强大,还有很多功能没来得及学习,希望以后能记录更多吧